Главная страница Случайная страница

КАТЕГОРИИ:

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Преобразователи уровней.

|

|

В электронной аппаратуре по разным причинам часто используется различная номенклатура дискретных (резисторы, конденсаторы, индуктивности, диоды, транзисторы), интегральных (МИС, СИС, БИС), конструктивных (клавиатура, кнопки, индикаторы) и других компонентов с различными статическими и динамическими характеристиками. Для обеспечения совместимости (согласования) этих компонентов по уровням сигналов, току, и другим характеристикам используются специальные элементы и схемные решения.

Преобразователями уровней называют специальные элементы цифровых устройств, предназначенные для согласования входных и выходных сигналов по напряжению и току при использовании в одном устройстве интегральных микросхем из различных семейств и с различными напряжениями питания. В связи с большим разнообразием компонентов электронных схем рассмотреть все варианты преобразователей уровня не представляется возможным. Ограничимся кратким рассмотрением самой типичной ситуации – одновременное использование элементов КМОП, работающих при более высоком однополярном напряжении питания, и ТТЛ(Ш). Уровень логической единицы в таких КМОП схемах выше, чем у ТТЛ(Ш), а максимальный выходной ток ниже. Поэтому при подключении входов ТТЛ(Ш) схем к выходам КМОП схем должно сопровождаться понижением до необходимого уровня логической единицы и согласованием по току. В сочетании выходы ТТЛ(Ш) – входы КМОП напряжение высокого уровня, формируемое ТТЛ(Ш), обычно недостаточно для надлежащего управления КМОП и должно быть увеличено.

Для этой цели в составе многих серий ИМС ТТЛ(Ш), КМОП малой степени интеграции имеются микросхемы-преобразователи уровня, предназначенные для согласования только уровня напряжения или тока или уровня напряжения и тока одновременно. Они могут быть понижающими или повышающими или универсальными, которые можно использовать как для понижения так и повышения уровней напряжения.

Среди них:

· преобразователи КМОП-ТТЛ - 1561ПУ4, 1561ЛН1;

· преобразователи ТТЛ-КМОП - 1533ПУ7, 1533ПУ8, 1533ЛН3, 1533ЛН5.

· Универсальный преобразователь 564(1564)ПУ6 (уровень входных сигналов определяется вторым напряжением питания).

Если необходимо разработать специальный преобразователь уровня, то можно использовать делители напряжения, ключевые транзисторные схемы, схемы с открытым коллектором, оптоэлектронные элементы и др. [ ].

Комбинационные арифметико-логические устройства (КАЛУ)

Наряду с выполнением арифметических операций сложения, вычитания, реже умножения и деления, приходится выполнять логические операции, причем если Х=(х3, х2, х1, х0), Y=(y3, y2, y1, y0), то Х*Y=(х3* y3, х2* y2, х1* y1, х0* y0), где * - любая логическая операция, то есть логические операции выполняются поразрядно.

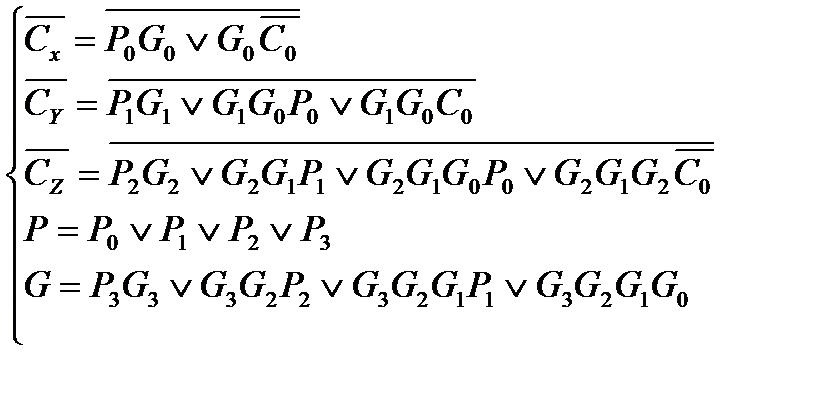

Для уменьшения затрат оборудования при построении блоков, реализующих арифметические и логические операции, были созданы интегральные микросхемы комбинационных арифметико-логических устройств КАЛУ (ALU, Arithmetic-Logic Unit). В основе функционирования и внутренней структуры КАЛУ лежит следующая система из 11 уравнений:

F – информационные выходы;

Ai, Bi - информационные входы;

Si – управляющий вход (настройка на реализацию конкретной логической или арифметической операции);

ai, bi – промежуточные переменные;

qi – уравнения формирования параллельного переноса в 4-разрядной секции;

М (Mode) – вход управления, задающий тип реализуемой операции;

С0 – входной перенос;

C4 – выходной перенос;

P – выход распространения переноса (прозрачности);

G – выход генерации переноса;

E – выход равенства операндов (с открытым коллектором);

В схеме реализующей эти уравнения три каскада. Первый каскад реализует уравнения 2, 3; второй каскад - уравнения 4-7, 10; третий каскад- уравнения 1, 8, 11. Данная система уравнений лежит в основе функциональной организации большинства КАЛУ в составе серий интегральных микросхем ТТЛ, ТТЛШ малой степени интеграции. Например, микросхема 1533 ИП3, условное графическое обозначение которой приведено ниже.

| В зависимости от комбинации сигналов на управляющих входах S1, M выполняется соответствующая логическая или арифметико-логическая операция. При М=0 реализуются арифметико-логические (логико-арифметические) операции (цепи переноса задействованы), при М=1 – логические операции (цепи переноса заблокированы). Результат операции считывается на выходах Fi. |

Например: при М=1 и S3S2S1S0=< 0000> по уравнениям системы можно проследить, что q0=q1=q2=q3=1, ai=0, bi=Аi, поэтому  , то есть выполняется логическая операция «Инверсия»; если же М=0, то все q задействованы и

, то есть выполняется логическая операция «Инверсия»; если же М=0, то все q задействованы и  .

.

Наличие пяти управляющих сигналов S0-S3, М, позволяет реализовать в таком КАЛУ 32 операции (16 арифметико-логических и 16 логических). Если учесть, что на комбинационную схему, кроме того, можно подать и инверсные значения операндов, то потенциально становится возможной реализация еще 32 операций для инверсной логики и общее количество реализуемых арифметических и логических операций может достигнуть 64. На самом деле часть реализуемых операций повторяется, поэтому количество различных реализуемых операций меньше. Все они приведены в таблице 1.

В логико-арифметических (или арифметико-логических) операциях встречаются и логические и арифметические операции одновременно. При этом запись вида

означает, что сначала поразрядно выполняются логические операции в скобках, а затем арифметическое сложение. В таблице 1 использованы обозначения: «0»=0000, «1»=1111, «С0»=000С0; `X и `Y – поразрядное инвертирование операндов X и Y, «V»- поразрядная дизъюнкция, «&»- поразрядная конъюнкция, «+» - арифметическая сумма.

Таблица 1.

| j | E3E2E1E0 | Прямые операнды | Инверсные операнды | ||

| M=0 Логико - арифметические операции. | M=1 Логические операции. | M=0 Логико - арифметические операции. | M=1 Логические операции. | ||

| Х+С0 | 1+Х+С0 | ` | |||

| (X V Y)+C0 | 1+(X& Y)+C0 | ||||

| 1+C0 | 1+C0 | ||||

| X+(X& Y)+C0 | X+(XVY)+C0 | ||||

| X+Y+C0 | X+Y+C0 | ||||

| Y | Y | ||||

| 1+(X& Y)+C0 | X& Y | (XVY)+C0 | XVY | ||

| X+X+C0 | X+X+C0 | ||||

| (XVY)+X+C0 | (X& Y)+X+C0 | ||||

| XVY | X& Y | ||||

| 1+X+C0 | X | X+C0 | X |

Условное графическое обозначение (УГ0) КАЛУ, приведенное выше, предполагает прямые значения операндов на входах. Для инверсных значений операндов на УГ0 поменяются местами знаки инверсий на входах и выходах С4, С0, ai, bi, Fi, PG.

На выходе «Е» КАЛУ можно получить признак равенства операндов X=Y, хотя в настройках в «чистом» виде эта операция отсутствует. В качестве настроек для этого следует использовать операцию равнозначности кодов

.

Для сравнения операндов можно использовать операцию вычитания (код настройки 0110). О соотношении чисел X и Y в этом случае можно судить по состоянию заёма С4, результаты сведены в таблицу 2.

Таблица 2.

| С0 | С4 | Операция | |

| Прямые операнды | Инверсные операнды | ||

| F(A≤ B) | F(A≥ B) | ||

| F(A> B) | F(A< B) | ||

| F(A< B) | F(A> B) | ||

| F(A≥ B) | F(A≤ B) |

В случае необходимости для увеличения разрядности используется каскадное включение нескольких микросхем КАЛУ. Если требования к быстродействию невысоки, то следует использовать последовательный перенос между секциями.

Например, структурная схема параллельного 12-разрядного КАЛУ с последовательным переносом между 4-разрядными секциями будет иметь вид:

Достоинства схемы - ее простота и отсутствие дополнительных элементов. Недостатки: невысокое быстродействие, уменьшающееся пропорционально количеству секций в схеме.

В тех случаях, когда требования к быстродействию высоки, в паре с несколькими АЛУ используется специальная схема ускоренного переноса (СУП). В основе функционирования СУП лежит система уравнений:

| Система для прямых значений операндов |

Условное графическое обозначение схемы ускоренного переноса представлено на рисунке:

Одна микросхема СУП обеспечивает параллельный перенос в 16-разрядном КАЛУ из четырех секций. Для инверсных значений операндов на входах-выходах УГ0 поменяются местами знаки инверсий. Структурная схема совместного подключения четырех КАЛУ и СУП будет иметь вид:

В схеме не показаны информационные каналы A, B, F, цепи управления S0-S3, М. Выходы P, G старшего КАЛУ можно не подключать, так как P3G3 не участвуют в формировании Cx, Cy, Cz. Однако, если выходы P, G СУП используются в последующих каскадах, то P3, G3 подключаются.

Для 64-разрядного параллельного КАЛУ с параллельным переносом схема совместного включения КАЛУ и СУП будет иметь вид:

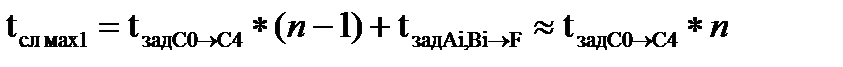

Время выполнения операции сложения в параллельном 16-разрядном КАЛУ с последовательным переносом отслеживается по формуле:

Для микросхем серии 1533 tсп мах1=26нс*4=104нс.

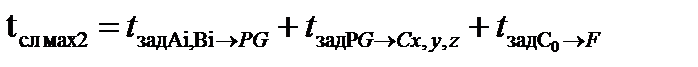

Для схемы такой же разрядности с параллельным переносом:

32нс+29нс+26нс=87нс

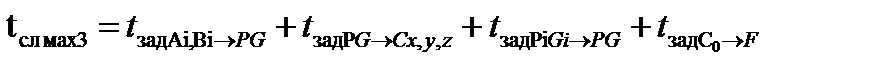

Для 64-разрядной схемы с параллельным переносом:

32нс+29нс+30нс+26нс=117нс

Для 64-разрядной схемы с последовательным переносом tсл=416нс. Таким образом, с увеличением разрядности выигрыш в быстродействии схемы с параллельным переносом становится все более ощутимым.