Главная страница Случайная страница

КАТЕГОРИИ:

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Пример программы

|

|

Структура программы на языке VHDL

Раздел ссылок

library ieee;

library lpm;

use ieee.std_logic_1164.all;

use ieee.arith.all;

use ieee.numeric_std.all;

usei eee.VITAL_Primitives.all;

use lpm.lpm_components.all;

Раздел интефейса

n -- N-разрядный счетчик

entity COUNT_N is

generic (N: integer: =8); --N- к-во разр.

port

(clk: in std_logic; -- вход синхронизации

s_clr: in std_logic; --вход синхр. сброса

ce: in std_logic; -- вход разреш. работы

c_per: out std_logic; -- вых. разр. перен.

q: out std_logic_vector(N downto 0));

--выход счетчика

end COUNT_N;

Раздел реализации

architecture behav of count_N is

signal cnt: std_logic_vector (L downto 0);

-- внутреннее состояние счетчика

BEGIN

< операторы языка описывающие данный вариант реализации счетчика>

END;

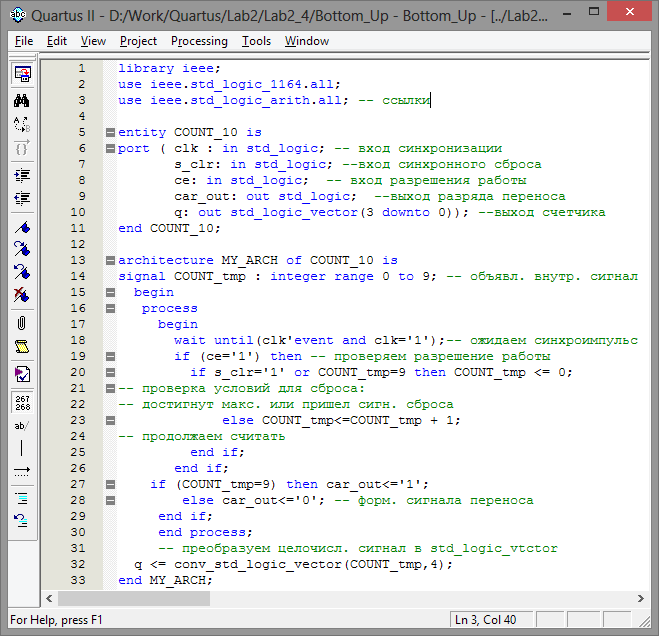

Пример программы

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

use IEEE.std_logic_arith.all;

entity counter8 is

generic (L: integer: =7);

port (clk, en, rst: in std_logic;

count: out std_logic_vector (L downto 0));

end counter8;

architecture behav of counter8 is

signal cnt: std_logic_vector (L downto 0);

begin

process (clk, en, cnt, rst)

begin

if (rst = '0') then

cnt < = (others => '0');

elsif (clk'event and clk = '1') then

if (en = '1') then

cnt < = cnt + '1';

end if;

end if;

end process;

count < = cnt;

end behav;