Главная страница Случайная страница

КАТЕГОРИИ:

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Введение. Курсовой проект по дисциплине

|

|

Курсовой проект по дисциплине

«Микросхемотехника»

«ЛОГИЧЕСКИЙ СИНТЕЗ ЦИФРОВЫХ УСТРОЙСТВ»

Вариант 1769

Выполнила:

Смирнова М.Л.

Группа:

06-А-1 (б)

Проверил:

Федюкин В.М.

Кострома

Содержание

1. Введение.

2. Описание работы проектируемого устройства.

3. Исходные данные.

4. Синтез комбинационной схемы.

5. Синтез логической функции в заданном базисе.

6. Расчет одновибратора.

7. Синтез счетчика.

8. Синтез дешифратора.

9. Спецификация.

10. Литература.

Введение.

Одна из основных тенденций развития современной техники — создание комплексных систем автоматизированного управления техническими объектами. В таких комплексах существенная часть информации циркулирует в дискретном виде.

Это информация о состоянии механизмов, агрегатов и установок (включено / выключено, в норме /не в норме), о положении арматуры трубопроводов (открыто / закрыто), это сигналы с конечных выключателей, командоаппаратов (контроллеров), кнопок и т.п. (цепь замкнута / разомкнута). Сигналы, вырабатываемые управляющими устройствами на основе этой информации, также имеют дискретный характер (включить / выключить, открыть/ закрыть).

Характерной особенностью этих сигналов является то, что нас не интересует их точное конкретное значение в какой-либо системе единиц, а интересует лишь факт наличия/отсутствия сигнала или превышения им некоторого порогового значения.

Поскольку сигналы имеют только два возможных состояния, то для их описания достаточно двух цифр - “0” и “1”, которыми кодируются эти состояния. Такие сигналы и функции, их описывающие, получили название логических.

Логические устройства получили в последние годы широкое распространение во многих областях техники. При этом все возрастающий объем функций, возлагаемых на автоматические устройства, в сочетании с использованием современного элементного базиса в виде больших и сверхбольших интегральных микросхем привели к существенному усложнению дискретных устройств. Это вызывает необходимость изучения научных методов проектирования логических устройств.

Доминирующая роль вычислительной техники, как основного “потребителя” методов синтеза дискретных устройств, привела к тому, что и сами методы, и литература, описывающая эти методы, ориентированы на специалистов по ЭВМ. В то же время, несмотря на общие основы методологии проектирования, логические устройства промышленной автоматики существенно отличаются от ЭВМ. Для них характерно большое число неиспользуемых состояний, широкое применение контактных элементов, наличие специальных режимов работы, невысокие требования к быстродействию и энергопотреблению, но высокие требования к надежности и др. Это требует индивидуального подхода при их проектировании.

Задание.

1. Описание работы проектируемого устройства.

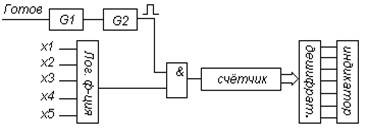

Объект представляет собой техническое устройство, в которое поступают различные детали. Имеются 5 датчиков, которые определяют соответствие деталей (" да" - " нет") некоторым параметрам (размер, форма, цвет, конфигурация и т.п.). В зависимости от комбинации сигналов датчиков f(X5, X4, X3, X2, X1) детали сортируются и направляются в разные бункеры и подсчитываются. Рассмотрим работу для одного бункера.

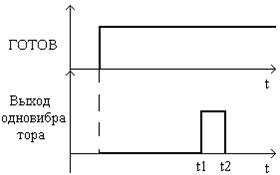

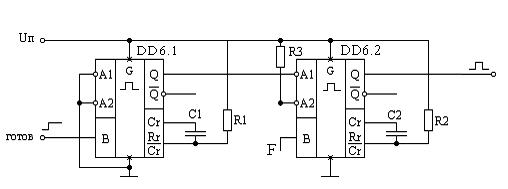

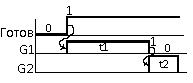

При поступлении детали в позицию сортировки вырабатывается сигнал ГОТОВ, который равен “1" все время нахождения детали в этой позиции. Для проектируемой схемы сигнал ГОТОВ и сигналы датчиков Х5, Х4, Х3, Х2, Х1 - внешние. По фронту сигнала ГОТОВ запускается одновибратор (G1, G2 - одновибраторы). Через время задержки t1 (на срабатывание датчиков) одновибратор формирует синхроимпульс длительностью t2. По сигналу " 1" на выходе комбинационной схемы и синхроимпульсу детали направляются в соответствующий бункер. Схема счетчика осуществляет подсчет деталей, поступающих в бункер, и при достижении заданного числа N выдает сигнал о заполнении бункера.

При поступлении детали в позицию сортировки вырабатывается сигнал ГОТОВ, который равен “1" все время нахождения детали в этой позиции. Для проектируемой схемы сигнал ГОТОВ и сигналы датчиков Х5, Х4, Х3, Х2, Х1 - внешние. По фронту сигнала ГОТОВ запускается одновибратор (G1, G2 - одновибраторы). Через время задержки t1 (на срабатывание датчиков) одновибратор формирует синхроимпульс длительностью t2. По сигналу " 1" на выходе комбинационной схемы и синхроимпульсу детали направляются в соответствующий бункер. Схема счетчика осуществляет подсчет деталей, поступающих в бункер, и при достижении заданного числа N выдает сигнал о заполнении бункера.

Курсовой проект должен содержать:

1. В соответствии с заданной таблицей состояний минимизировать логическую функцию и синтезировать её в заданном базисе;

2. Спроектировать одновибратор на интегральных таймерах для заданного времени задержки t1 и длительности импульса t2;

3. Синтезировать в заданном элементном базисе счётчик с заданным модулем счёта N и направлением счёта;

4. Разработать дешифратор для индикации показаний счётчика при заданном типе индикатора;

5. Выполнить чертёж разработанной схемы.

2. Исходные данные.

Модуль счета N и направление счета

| Модуль счета | Направление |

| прямое |

Базис элементов схемы

| Базис лог. функции и дешифратора | Базис счетчика | Тип индикатора |

| И, ИЛИ, НЕ | К555ТМ8 | АЛС342Б |

Параметры одновибратора

| T1, с | T2, нс. | Микросхема |

| 0.17 | К555АГ1 |

Варианты логической функции F(X5, X4, X3, X2, X1)

| Входной сигнал | Выход | |||||||

| № | X5 | X4 | X3 | X2 | X1 | F(X5, X4, X3, X2, X1) | ||

| х | ||||||||

| х | ||||||||

3. Синтез комбинационной схемы.

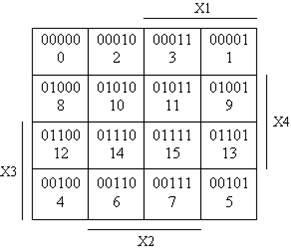

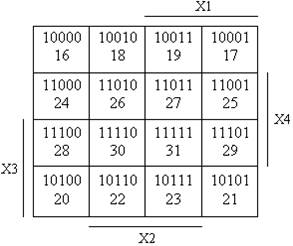

При небольшом числе переменных удобным и наглядным является графическое представление логической функции в виде карт минтермов или в виде карт Карно.

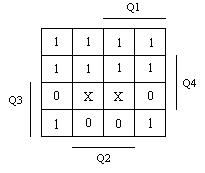

Карта Карно состоит из q=2n клеток, причем каждой из клеток соответствует один из q минтермов. Карта представляется в виде квадрата или прямоугольника. Переменные разбиваются на две группы. Переменным одной группы ставят в соответствие столбцы, другой - строки. Переменные первой группы остаются постоянными в пределах каждого столбца, второй - постоянными в пределах строки. Каждой клетке ставится в соответствие определенный набор переменных.

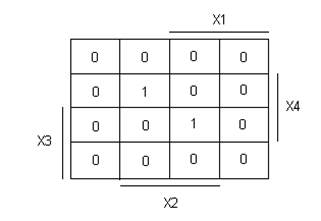

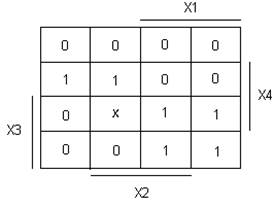

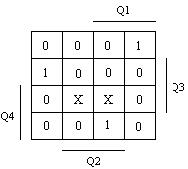

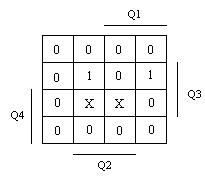

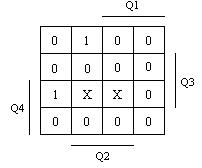

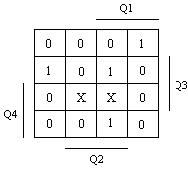

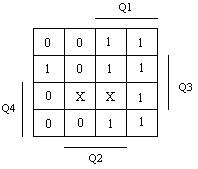

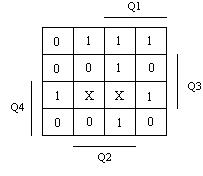

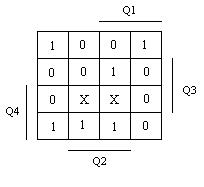

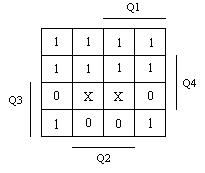

при X5=0 при X5=1

Общий вид карты Карно.

Карты Карно для пяти переменных.

Проведем минимизацию. Под задачей минимизации ЛФ понимается задача упрощения этих функций в целях уменьшения затрат на их аппаратурную реализацию. Минимальной будет считаться такая разновидность функции, которая состоит из наименьшего количества дизъюнктивных членов при наименьшем суммарном числе символов переменных. В основе методов минимизации ЛФ лежит операция склеивания, а в качестве исходной формы ЛФ, как правило, выбирают СДНФ.

Для минимизации ЛФ приводят к СДНФ и заполняют карту Карно. Наличие единиц в соседних (по вертикали или по горизонтали) клетках карты соответствует смежным минтермам, которые могут быть склеены. Процесс группировки двух, четырех, восьми и т.д. клеток с единицами удобно проводить визуально, что оформляется в виде прямоугольного контура вокруг этих клеток, после чего можно записать ответ - тупиковую ДНФ в виде дизъюнкции (суммы) простых импликант, описывающих проведенные контуры. При наличии различных вариантов проведения контуров получаем несколько тупиковых ДНФ, среди которых выбираем минимальную.

Минимизированная функция:

F =

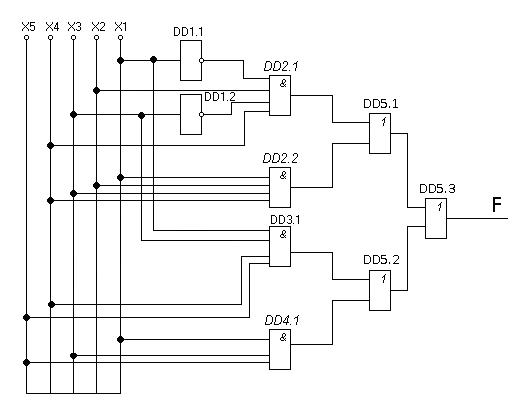

4. Синтез логической функции в заданном базисе.

Схема логической функции.

Логическая функция реализована на двух элементах “НЕ”, четырех элементах “И” и трех элементах “ИЛИ”,

5. Расчет одновибратора.

Согласно варианту задания, необходимо спроектировать устройство, которое обеспечивало бы выдержку времени для импульса в счётчик. Эта задержка нужна потому, что сигналы от датчиков приходят не одновременно и поэтому может получится неверный результат для счётчика. В данном случае этим устройством является одновибратор, а точнее два одновибратора: первый вырабатывает импульс задержки, а второй вырабатывает короткий импульс для счётчика и срабатывает по спаду импульса первого одновибратора.

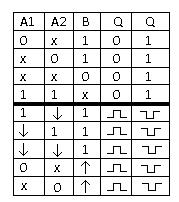

Параметры одновибратора: T1=0.0, 17с, T2=75мс, микросхема К555АГ1. К555АГ1 – ждущий мультивибратор. Содержит внутреннюю ячейку памяти с выходами Q и инверсным Q. Мультивибратор один раз может ‘выстрелить’, если хотя бы на один из входов поступил перепад: отрицательный на A1 или A2, положительный - на B. Входов запуска три: инверсные A1, A2 и прямой B. Окончание импульса (внутренний сброс) определяется внешним конденсатором C и R (есть и внутренний резистор Rвн=2кОм).

(1)

(1)

Расчет номиналов элементов схемы (сопротивлений – R1, R2, конденсаторов – C1, C2):

R1 = 22 кОм воспользовавшись формулой (1) рассчитаем С

С=  =1, 103

=1, 103

получим C1 = 1, 103 мкФ, возьмем стандартное ближайшее значение: C1 = 1, 3 мкФ, при этом получим действительное время задержки T1 = 0.02сек.

R2 = 22 кОм воспользовавшись формулой (1) рассчитаем С

С=  =4, 87

=4, 87

получим C2 = 4, 87 мкФ, возьмем стандартное ближайшее значение из ряда Е12: C2 = 4, 7 мк Ф, при этом получим действительное время задержки T2 = 72 мс.

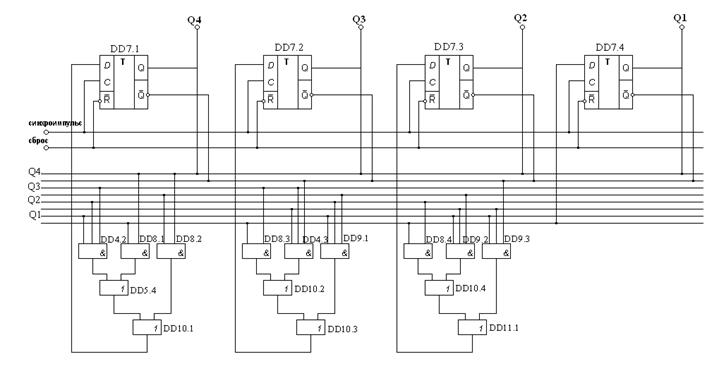

6. Синтез счетчика.

Разработаем счётчик - устройство, которое считает все пришедшие импульсы до тех пор, пока их количество не дойдет до некоторой величины, называемой модулем счёта. Модуль счёта для моего варианта равен 14. Значит, для того, чтобы синтезировать счётчик надо четыре триггера. Т.к. триггер имеет два устойчивых состояния, следовательно, четыре триггера могут дать шестнадцать разных комбинаций этих состояний. Как только счётчик дойдёт до величины модуля счёта, то он сбрасывается в исходное сотстояние. А исходное состояние определяется направлением счёта. Если направление прямое, то начинаем с нуля и до модуля счёта.

В зависимости от вида перехода и типа элемента памяти формируется таблица возбуждения (словарь переходов) элементов памяти (триггеров).

Словарь переходов триггера:

| Вид перехода | D |

| 0®0 | |

| 0®1 | |

| 1®0 | |

| 1®1 |

Таблица состояний и переходов.

| Первый | Следующий | |||||||||||||||

| I | Q4 | Q3 | Q2 | Q1 | Q4 | Q3 | Q2 | Q1 | ® | D4 | ® | D3 | ® | D2 | ® | D1 |

| 0-0 | 0-0 | 0-0 | 0-1 | |||||||||||||

| 0-0 | 0-0 | 0-1 | 1-0 | |||||||||||||

| 0-0 | 0-0 | 1-1 | 0-1 | |||||||||||||

| 0-0 | 0-1 | 1-0 | 1-0 | |||||||||||||

| 0-0 | 1-1 | 0-0 | 0-1 | |||||||||||||

| 0-0 | 1-1 | 0-1 | 1-0 | |||||||||||||

| 0-0 | 1-1 | 1-1 | 0-1 | |||||||||||||

| 0-1 | 1-0 | 1-0 | 1-0 | |||||||||||||

| 1-1 | 0-0 | 0-0 | 0-1 | |||||||||||||

| 1-1 | 0-0 | 0-1 | 1-0 | |||||||||||||

| 1-1 | 0-0 | 1-1 | 0-1 | |||||||||||||

| 1-1 | 0-1 | 1-0 | 1-0 | |||||||||||||

| 1-1 | 1-1 | 0-0 | 0-1 | |||||||||||||

| 1-0 | 1-0 | 0-0 | 1-0 |

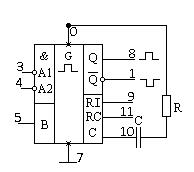

Базисом счетчика является микросхема К555ТМ8. Некоторые сведения о ней приведены в таблице

Таблица

| Микро-схема | Вид триггера | Число триггеров | Средняя задержка, нс | Частота переключе-ния, МГц | Потребля-емая мощность, мВт | Напряжение питания, В |

| К555ТМ8 | D |

Счетчик будет состоять из четырех D-триггеров.

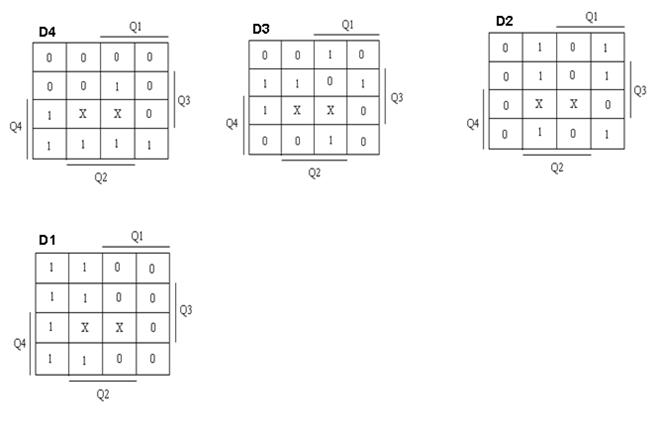

Для логического синтеза комбинационной схемы воспользуемся картами Карно.

Схема счетчика

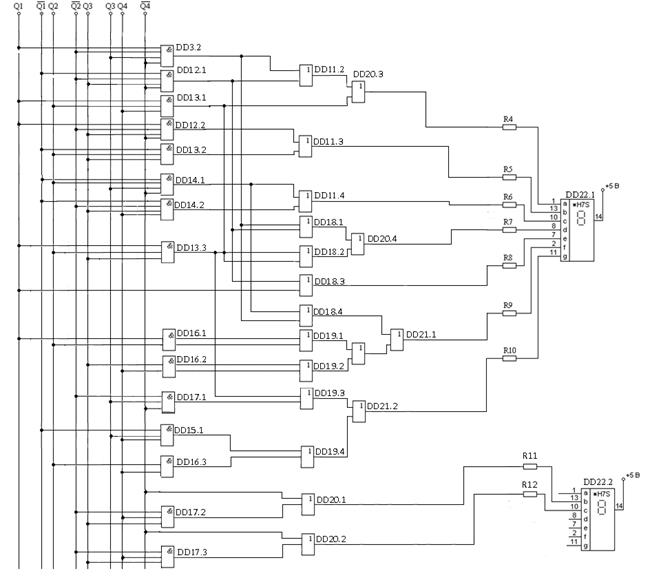

7. Синтез дешифратора.

Разработаем устройство, которое позволяет увидеть число, которое выдаст счётчик. Со счётчика мы получаем некоторое двоичное число, которое при помощи дешифратора переводим в такую форму, чтобы его можно было вывести на индикатор АЛС342Б.

С выхода счётчика мы получим 4-х разрядное число, а индикатор у нас является семисегментным. Т.о. 4-х разрядное число необходимо преобразовать в 7-ми разрядное. Для каждого сегмента поставим в соответствие некоторую логическую функцию. Таких функций всего 7 (т.к. 7 сегментов). Заполним таблицу для этих логических функций A..G. Входными величинами являются разряды счётчика Q1..Q4. Заполнять будем таким образом: если для данного двоичного числа на индикаторе данный сегмент должен светиться, то необходимо подать на него " 0", иначе " 1".

С выхода счётчика мы получим 4-х разрядное число, а индикатор у нас является семисегментным. Т.о. 4-х разрядное число необходимо преобразовать в 7-ми разрядное. Для каждого сегмента поставим в соответствие некоторую логическую функцию. Таких функций всего 7 (т.к. 7 сегментов). Заполним таблицу для этих логических функций A..G. Входными величинами являются разряды счётчика Q1..Q4. Заполнять будем таким образом: если для данного двоичного числа на индикаторе данный сегмент должен светиться, то необходимо подать на него " 0", иначе " 1".

Таблица сигнализации индикатора АЛС342Б с общим анодом.

| I | Q4 | Q3 | Q2 | Q1 | A | B | C | D | E | F | G | В1 | С1 |

A B C

D E

F G

B1 C1

В1=

С1=

Низкий логический уровень подается на соответствующие входы микросхемы DD21 и DD11, для ограничения тока на входах данных микросхем стоят сопротивления, рассчитаные на выходной ток нуля микросхемы К531ЛЛ1 (ЛИ3) 20мА, и падение напряжения на резисторе 0, 2В (т.к. на индикаторе падение напряжения 3.5В). Величина сопротивления резистора 65 Ом.

Схема дешифратора

| Поз. обозначение | Наименование | Кол. | Примечание | |||||||||||

| Резисторы ГОСТ 11.076-69 | ||||||||||||||

| R1 | МЛТ-0.5-22 кОм ±10% | |||||||||||||

| R2 | МЛТ-0.5-22 кОм ±10% | |||||||||||||

| R3 | МЛТ-1-1 кОм ±10% | |||||||||||||

| R4, R5, R6, R7, R8, R9, R10, R11, R12 | МЛТ-0.5-68 Ом ±10% | |||||||||||||

| Конденсаторы ГОСТ 2.728-74 | ||||||||||||||

| C1 | КД-101-1.3 мкФ ±10% | |||||||||||||

| С2 | КД-101-4.7 мкФ ±10% | |||||||||||||

| Логические микросхемы ГОСТ 2.743-82 | ||||||||||||||

| DD1 | К555ЛН1 | |||||||||||||

| DD2, DD3, DD12, DD14 | К555ЛИ6 | |||||||||||||

| DD4, DD9, DD13, DD15, DD17 | К555ЛИ3 | |||||||||||||

| DD8, DD16 | К555ЛИ1 | |||||||||||||

| DD5, DD10, DD11, DD18, DD19, DD20, DD21 | К531ЛЛ1 | |||||||||||||

| Мультивибраторы | ||||||||||||||

| DD6 | К555АГ1 | |||||||||||||

| Триггеры | ||||||||||||||

| DD7 | К555ТМ8 | |||||||||||||

| Индикаторы ГОСТ 2.764-86 | ||||||||||||||

| DD22 | АЛС342Б | |||||||||||||

| ||||||||||||||

| Лит. | Масса | Масшт | ||||||||||||

| № докум. | Подп. | Дата | ||||||||||||

| Разраб. | Смирнова | |||||||||||||

| Провер. | Федюкин В.М. | Лист | Листов | |||||||||||

ЛИТЕРАТУРА

1. Шило В.Л. Популярные микросхемы ТТЛ. – М.: Аргус, 1993.

2. Алексеенко А.Г., Шагурин И.И. Микросхемотехника. - М.: Радио и связь, 1987.

3. В.М. Федюкин Основы логического синтеза цифровых устройств – Кострома 1999.

|