Главная страница Случайная страница

КАТЕГОРИИ:

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

SN – коммутационное поле

|

|

CCNC – управляющее устройство сети ОКС

SSNC – сетевой контроллер системы сигнализации

MB – буфер сообщений

CP – координационный процессор

CCG – центральный генератор тактовой частоты

PDC, SDC – линии первичного и вторичного уплотнения

CAS – сигнализация по выделенному сигнальному каналу

CCS – общеканальная сигнализация

Рисунок 4.8– Базовая структура ЦСК EWSD

Рисунок 4.9– Функциональная структура программного обеспечения

Программы операционной системы организуют работу всех программ в многопрограммном режиме и управляют вводом/выводом сообщений с внешних устройств (устройств машинной периферии).

Прикладное ПО обеспечивает обработку вызовов и реализацию функций технической эксплуатации (техническое обслуживание и административное управление).

Программы защиты и технического обслуживания гарантируют эксплуатацию системы без существенных нарушений ее качественных характеристик.

Аппаратные средства системы EWSD подразделяются на подсистемы доступа, коммутации, сигнализации, администрирования и управления.

4.2.2 Электронная управляющая система имеет иерархическую структуру (рисунок 4.10).

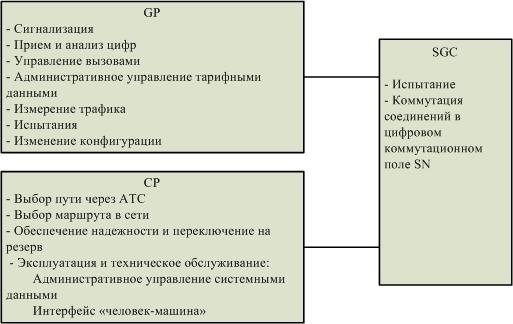

Верхний уровень управления представлен координационным процессором CP, который взаимодействует с групповыми процессорами GP линейных групп через каналы коммутационного поля. Распределение функций между CP и GP показано на рисунке 4.11. Для организации взаимодействия CP и GP в линии SDC каждой линейной группы выделен нулевой канал. Процессор GP, в свою очередь, взаимодействует с контроллерами абонентских блоков через каналы 64 кбит/c линий PDC.

CP – координационный процессор

MB – буфер сообщений

SN – коммутационное поле

GP – групповой процессор

LTG – линейная группа

DLUC – контроллер абонентского блока

SLMCP – процессор абонентского модуля

DLU – абонентский блок

SGC – процессор коммутационной группы

Рисунок 4.10– Структура управляющей системы

Рисунок 4.11 – Распределение функций между CP и GP

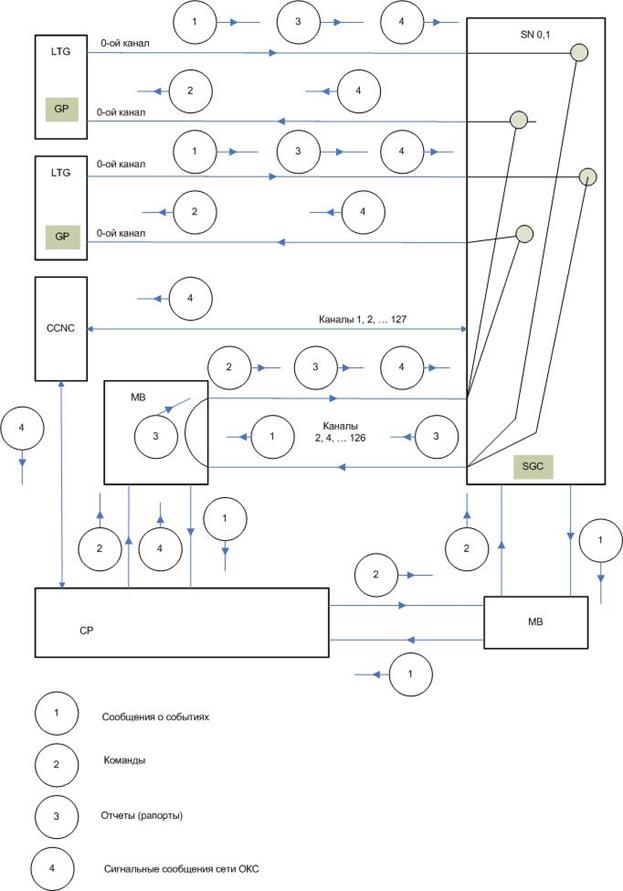

Рисунок 4.12 – Взаимодействие CP и GP

Все устройства соединяются с полем SN по линиям SDC с потоком 8, 192 Мбит/c (128 каналов по 64 кбит/c каждый). Нулевые каналы SDC задействуются для образования внутренних каналов передачи данных между GP разных LTG, между GP и СР (рисунок 4.12). Управление межпроцессорным обменом обеспечивает буфер сообщений МВ.

По внутренним каналам межпроцессорного обмена передаются следующие виды данных:

· сообщения о событиях (от GP LTG к CP, от SGC к СР);

· команды – указания на действия (от CP к GP LTG, от СР к SGC);

· рапорты – квитанции (отчеты) о выполненных действиях (между GP разных LTG);

· сигнальные сообщения ОКС№7 (между CP и ССNC, между GP LTG и CCNC).

Каждый GP LTG отправляет свои сообщения и рапорты в нулевом канале SDC. В коммутационном поле эта информация от 63-х LTG мультиплексируется в 2, 4 …126 каналы и поступает в буфер сообщений МВ, который производит сортировку данных. Сообщения о событиях направляются в CP, а рапорты, по возможности, перенаправляются в LTG, минуя СР.

Сигнальным трафиком ОКС№7 управляет CCNC, который выполняет функции подсистемы передачи сообщений МТР, а также часть функций подсистемы управления сигнальным соединением SCCP. При использовании SSNC (сетевой контроллер системы сигнализации) все сигнальные сообщения ОКС№7 обрабатываются без участия СР.

4.2.3 Процессор СР113 представляет собой мультипроцессор, производительность которого наращивается ступенями, благодаря чему он может обеспечить координацию работы станций любой емкости с соответствующей пропускной способностью. В системе EWSD V.15 используются два типа координационных процессора CP113D и CP113C/CR. Процессоры CP113C/CR входят в состав станций большой емкости в сочетании с буфером сообщений MBD, коммутационным полем SN(D) и контроллером системы сигнализации ОКС№7 SSNC. Процессоры CP113D применяются на станциях меньшей емкости в сочетании с буфером сообщений МВВ, коммутационным полем SN(B) и управляющим устройством сигнализации ОКС№7 CCNC.

Координационный процессор CP выполняет функции обработки вызовов, технической эксплуатации, обеспечения надежности.

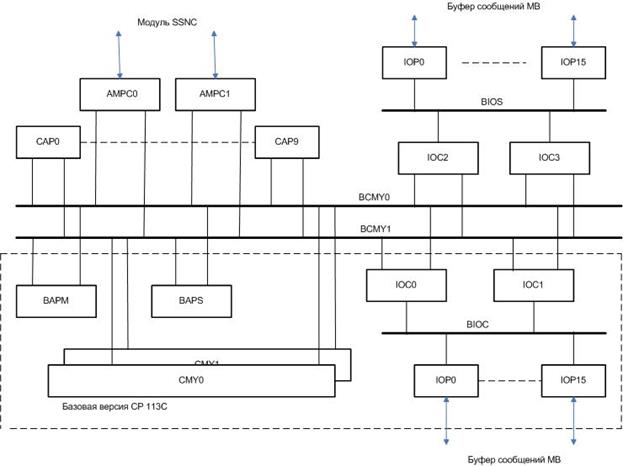

В состав CP входят (рисунок 4.13):

· BAP – базовый процессор, выполняющий функции обработки вызовов и технической эксплуатации;

· CAP – сопроцессор обработки вызовов;

· IOP – процессор ввода/вывода, управляет обменом данными с оборудованием коммутационной станции и периферийными устройствами технической эксплуатации ОА& М;

· CMY – общая память для хранения общей базы данных, списков ввода/выводадля интерфейсовIOP: MB и информации, используемой процессорами IOP для обмена данными с периферийными устройствами технической эксплуатации ОА& М;

· BCMY – шина общей памяти для межпроцессорной связи и реализации процедур обращения кCMY;

· IOC – контроллер ввода/вывода, образует интерфейс между шиной общей памятиBCMY и процессором IOP.

Кроме того, CP113C/CR содержит мостовой АТМ-процессор (процессор асинхронного режима передачи) типа C (АМРС), который является интерфейсом с сетевым контроллером SSNC.

Для повышения надежности все наиболее важные блоки координационного процессора дублируются.

AMPC – интерфейс сети АТМ (мостовой АТМ-процессор типа С)

CAP – сопроцессор (процессор обработки вызовов)

BAPM – основной (базовый) ведущий процессор

BAPS – основной (базовый) ведомый процессор

CMY – общая память

IOP – процессор ввода-вывода

IOC – контроллер ввода-вывода

BCMY – шина общей памяти

BIOC, BIOS –шины контроллеров ввода-вывода

Рисунок 4.13 –Структура процессора СР113С

Конфигурация координационного процессора зависит от требуемой производительности (таблица 4.3).

Таблица 4.3 – Комплектация CP 113

| Виды процессоров | Тип CP 113 | ||

| CP 113С | CP 113D | CP 113CR | |

| Максимальное количество процессоров | |||

| BAP | |||

| CAP | - | ||

| IOC | |||

| IOP | |||

| АМРС |

Во всех конфигурациях присутствуют два основных процессора ВАР:

· ведущий ВАРМ, выполняющий функции обработки вызовов и технической эксплуатации,

· ведомый ВАРS, который в нормальном режиме выполняет функции только обработки вызовов.