Главная страница Случайная страница

КАТЕГОРИИ:

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Канали вводу/виводу

|

|

План

1 Паралельна передача даних

1.1 Паралельний інтерфейс виводу в ЗП

1.2 Паралельний інтерфейс вводу із ЗП

2 Послідовна передача даних

2.1 Синхронний послідовний інтерфейс

2.2 Асинхронний послідовний інтерфейс

1.1 Паралельна передача даних між контролером і ЗП є по своїй організації є найбільш простим способом обміну. Для організації паралельної передачі даних крім шини даних, кількість ліній у якій дорівнює числу одночасно переданих бітів даних, використовується мінімальна кількість керуючих сигналів.

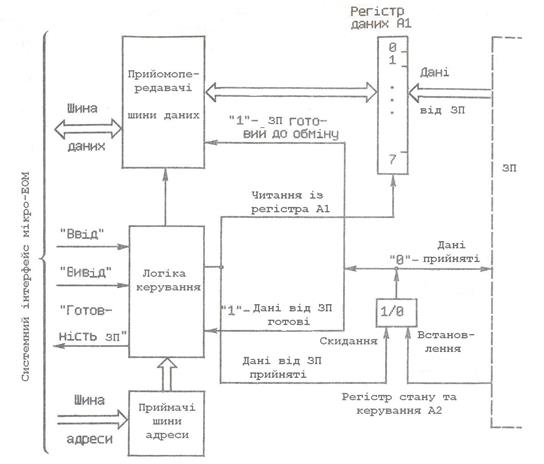

У простому контролері ЗП, що забезпечує побайтну передачу даних у зовнішній пристрій (рис. 65.1), у шині зв'язку з ЗП використовуються всього два керуючі сигналу - " Вихідні дані готові" й " Дані прийняті".

Для формування керуючого сигналу " Вихідні дані готові" і прийому із ЗП керуючого сигналу " Дані прийняті" у контролері використовується однорозрядний адресуємий регістр стану й керування А2. Одночасно із записом чергового байта даних із шини даних системного інтерфейсу в адресуємий регістр даних контролера (порт виводу А1) у регістр стану й керування записується логічна одиниця. Тим самим формується керуючий сигнал " Вихідні дані готові" у шині зв'язку з ЗП.

ЗП, прийнявши байт даних, керуючим сигналом " Дані прийняті" скидає регістр стану контролера в «нуль». При цьому формуються:

- керуючий сигнал системного інтерфейсу " Готовність ЗП";

- ознака готовності ЗП до обміну, передана у процесор по одній з ліній шини даних системного інтерфейсу за допомогою стандартної операції вводу при реалізації програми асинхронного обміну.

Логіка управління контролера забезпечує селекцію адрес регістрів контролера, прийом керуючих сигналів системного інтерфейсу й формування на їхній основі внутрішніх керуючих сигналів контролера, формування керуючого сигналу системного інтерфейсу " Готовність ЗП". Для сполучення регістрів контролера із шинами адреси й даних системного інтерфейсу в контролері використовуються приймачі шини адреси й прийомопередавачі шини даних.

Розглянемо на прикладі, яким образом контролер ЗП забезпечує паралельну передачу даних у ЗП під управлінням програми асинхронного обміну. Алгоритм асинхронного обміну в цьому випадку передачі простий.

1. Процесор мікро-ЕОМ перевіряє готовність ЗП до прийому даних.

2. Якщо ЗП готово до прийому даних (логічний 0 у регістрі А2), то дані передаються із шини даних системного інтерфейсу в регістр даних А1 контролера й далі у ЗП. Інакше повторюється п. 1.

1.2 Розглянемо блок-схему простого контролера ЗП (паралельного інтерфейсу), що забезпечує побайтний прийом даних із ЗП (рис. 65.2). У цьому контролері при взаємодії із зовнішнім пристроєм також використовуються два керуючі сигналу - " Дані від ЗП готові" й " Дані прийняті".

Для формування керуючого сигналу " Дані прийняті" і прийому із ЗП керуючого сигналу " Дані від ЗП готові" використовується однорозрядний адресуємий регістр стану й керування А2.

ЗП записує в регістр даних контролера А1 черговий байт даних і керуючим сигналом " Дані від ЗП готові" встановлює в одиницю регістр стану й керування А2.

При цьому формуються:

- керуючий сигнал системного інтерфейсу " Готовність ЗП";

- ознака готовності ЗП до обміну, що передається в процесор по одній із ліній шини даних системного інтерфейсу за допомогою операції вводу при реалізації програми асинхронного обміну.

Тим самим контролер сповіщає процесор про готовність даних у регістрі А1. Процесор, виконуючи програму асинхронного обміну, читає байт даних з регістра даних контролера й скидає в нуль регістр стану й керування А2. При цьому формується керуючий сигнал " Дані прийняті" у шині зв'язку із ЗП.

Логіка управління контролера й прийомопередавачі шин системного інтерфейсу виконують ті ж функції, що й у контролері виводу.

Розглянемо роботу паралельного інтерфейсу вводу при реалізації програми асинхронного обміну. Алгоритм асинхронного вводу так само простий, як й асинхронного виводу.

1. Процесор перевіряє наявність даних у регістрі даних контролера А1.

2. Якщо дані готові (логічна 1 у регістрі А2), то вони передаються з регістра даних А1 у шину даних системного інтерфейсу й далі в регістр процесора або осередок пам'яті мікро-ЕОМ. Інакше повторюється п. 1.

Як видно з розглянутих прикладів, для прийому або передачі одного байта даних процесору необхідно виконати всього кілька команд, час здійснення яких і визначає максимально досяжну швидкість обміну даними при паралельній передачі. При цьому час обробки байта даних в електронних схемах контролера можна не враховувати, тому що воно істотно менше часу виконання однієї команди процесора. Таким чином, при паралельній передачі забезпечується досить висока швидкість обміну даними. Найчастіше вона досягає сотень кілобайтів у секунду й на практиці обмежується тільки швидкодією ЗП.

Простота реалізації й висока швидкість обміну, властиві паралельній передачі даних, забезпечили широке поширення цього способу обміну даними із зовнішніми пристроями в ЕОМ. Сучасні мікро-ЕОМ оснащують широким набором універсальних паралельних інтерфейсів. Паралельні інтерфейси випускають й у вигляді окремих ВІС. Типовим прикладом такої ВІС є ВІС КР580ВВ55.

Приклад 1. Фрагмент програми передачі байта даних в асинхронному режимі з використанням паралельного інтерфейсу (контролер ЗП, рис. 65.1):

M1: TST @ # А2 - перевірка вмісту регістра А2, тобто готовності ЗП до прийому даних. При виконанні команди процесор по шині адреси передає в контролер адресу А2, супроводжуючи його сигналом " Ввід". Логіка управління контролера, реагуючи на ці сигнали, забезпечує передачу в процесор вмісту регістра стану й керування А2 по одній з ліній шини даних системного інтерфейсу (наприклад, це може бути старший - 15-й розряд шини даних).

// TST – команда перевірки (встановлення кодів умов у відповідності із вмістом перевіряємого регістру (в даному випадку А2));

@ # А2 – абсолютна адресація (виконавча адреса знаходиться черговому слові команди)//

BMІ M1 - перехід, якщо мінус. Процесор перевіряє значення старшого (знакового) розряду прийнятого слова даних. Одиниця в старшому розряді (знак мінус) указує на неготовність ЗП до прийому даних й, отже, на необхідність повернення до перевірки вмісту А2, тобто процесор, виконуючи дві перші команди, очікує готовності ЗП до прийому даних. Нуль у старшому розряді підтверджує готовність ЗП й, отже, можливість передачі байта даних.

MOV R1, @ # А1 - пересилання даних з регістра R1 процесора в регістр даних контролера A1. Процесор по шині адреси передає в контролер адресу А1, а по шині даних - байт даних, супроводжуючи їхнім сигналом " Вивід". Логіка управління контролера забезпечує запис байта даних із шини даних у регістр даних А1 і встановлює в «одиницю» регістр стану й керування А2, формуючи тим самим керуючий сигнал для ЗП " Вихідні дані готові". ЗП приймає байт даних і керуючим сигналом " Дані прийняті" скидає регістр стану й керування А2 в «нуль». Контролер ЗП за цим сигналом формує й передає в процесор сигнал " Готовність ЗП", що у цьому випадку сповіщає процесор про прийом байта даних зовнішнім пристроєм і завершує цикл виводу даних у команді пересилання.

Приклад 8.2. Фрагмент програми прийому байта даних в асинхронному режимі з використанням паралельного інтерфейсу (контролер ЗП, рис. 65.2):

M1: TST @ # А2 - перевірка вмісту регістра А2, тобто ознаки наявності даних у регістрі даних А1. Команда виконується точно так само, як і перша команда в прикладі 1.

BPL M1 - перехід, якщо плюс. Процесор перевіряє значення старшого (знакового) розряду прийнятого слова даних. Одиниця в знаковому розряді (вміст регістра А2) підтверджує, що дані від ЗП записані в регістр даних контролера й необхідно переслати їх у шину даних. Нуль у знаковому розряді вказує на неготовність даних від ЗП й, отже, на необхідність повернутися до перевірки готовності (команда TST @# A2).

MOV @ # A1, R1 - пересилка даних з регістра даних контролера А1 у регістр R1 процесора. Процесор передає в контролер по шині адреси системного інтерфейсу адресу А1, супроводжуючи його сигналом " Ввід". Логіка управління контролера у відповідь на сигнал " Ввід" забезпечує передачу байта даних з регістра даних А1 на шину даних, супроводжуючи їхнім сигналом " Готовність ЗП", що підтверджує наявність даних від ЗП на шині даних. Потім логіка керування скидає в нуль регістр стану й керування А2, формуючи тим самим керуючий сигнал для ЗП " Дані прийняті". Таким способом завершується цикл вводу даних у команді пересилання.

Домашнє завдання:

[5] С. 174-177.

2 Використання послідовних ліній зв'язку для обміну даними із ЗП покладає на контролери ЗП додаткові (в порівнянні з контролерами для паралельного обміну) функції. По-перше, виникає необхідність перетворення формату даних: з паралельного формату, у якому вони надходять у контролер ЗП із системного інтерфейсу мікро-ЕОМ, у послідовний при передачі у ЗП й з послідовного в паралельний при прийомі даних з ЗП. По-друге, потрібно реалізувати відповідний режиму роботи ЗП спосіб обміну даними: синхронний або асинхронний.

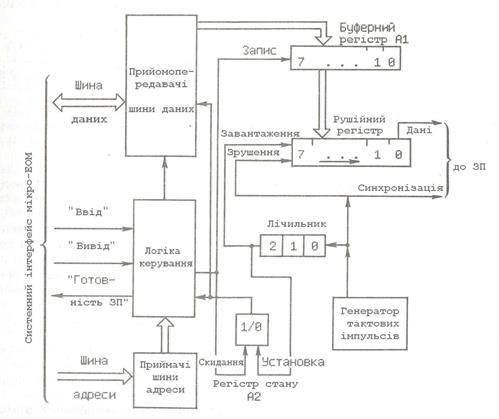

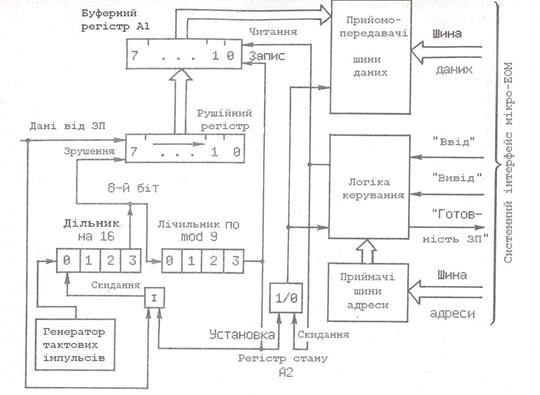

2.1 Розглянемо контролер для синхронної передачі даних у ЗП по послідовній лінії зв'язку (послідовний інтерфейс) (рис. 66.1).

Восьмирозрядний адресуємий буферний регістр контролера А1 служить для тимчасового зберігання байта даних до його завантаження у рушійний регістр. Запис байта даних у буферний регістр із шини даних системного інтерфейсу виконується так само, як й у паралельному інтерфейсі, тільки при наявності одиниці в однорозрядному адресуємому регістрі стану контролера А2. Одиниця в регістрі стану вказує на готовність контролера прийняти черговий байт у буферний регістр. Вміст регістра А2 передається в процесор по одній з ліній шини даних системного інтерфейсу й використовується для формування керуючого сигналу системного інтерфейсу " Готовність ЗП". При записі чергового байта в буферний регістр А1 скидається в нуль регістр стану А2.

Перетворення даних з паралельного формату, у якому вони надійшли у буферний регістр контролера із системного інтерфейсу, у послідовний і передача їх у лінію зв'язку виконуються у рушійному регістрі за допомогою генератора тактових імпульсів і двійкового трьохрозрядного лічильника імпульсів наступним чином.

Послідовна лінія зв'язку контролера із ЗП підключається до виходу молодшого розряду рушійного регістра. По черговому тактовому імпульсі вміст рушійного регістра зрушується на один розряд вправо й у лінію зв'язку " Дані" видається значення чергового розряду. Одночасно зі зрушенням у ЗП передається по окремій лінії " Синхронізація" тактовий імпульс. Таким чином, кожен переданий по лінії " Дані" біт інформації супроводжується синхронізуючим сигналом по лінії " Синхронізація", що забезпечує його однозначне сприйняття на прийомному кінці послідовної лінії зв'язку.

Кількість переданих у лінію тактових сигналів, а отже, і переданих біт інформації підраховується лічильником тактових імпульсів. Як тільки вміст лічильника стає рівним 7, тобто в лінію переданий 8 біт (1 байт) інформації, формується керуючий сигнал " Завантаження", що забезпечує запис у рушійний регістр чергового байта з буферного регістра. Цим же керуючим сигналом встановлюється в " 1" регістр стану. Черговим тактовим імпульсом лічильник буде скинутий в " 0", і почнеться черговий цикл видачі восьми бітів інформації з рушійного регістра в лінію зв'язку.

Синхронна послідовна передача окремих бітів даних у лінію зв'язку повинна виконуватися без якої-небудь перерви, і наступний байт даних повинен бути завантажений у буферний регістр із системного інтерфейсу за час, що не перевищує часу передачі восьми бітів у послідовну лінію зв'язку.

При записі байта даних у буферний регістр скидається в нуль регістр стану контролера. Нуль у цьому регістрі вказує, що в лінію зв'язку передається байт даних з рушійного регістра, а наступний переданий байт даних завантажений у рушійний регістр.

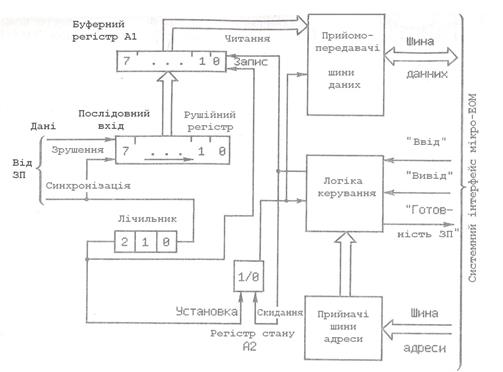

Контролер для послідовного синхронного прийому даних із ЗП (рис. 66.2) складається з тих же компонентів, що й контролер для синхронної послідовної передачі, за винятком генератора тактових імпульсів.

Буферний регістр контролера А1 служить для тимчасового зберігання байта даних, що надійшов з рушійного регістра. Читання байта даних у системний інтерфейс із буферного регістра виконується так само, як й у паралельному інтерфейсі. Одиниця в регістрі стану контролера А2 вказує на готовність контролера передати черговий байт даних у системний інтерфейс.

Дані, що надходять із лінії зв'язку в послідовному коді, перетворяться в контролері в паралельний код за допомогою рушійного регістра й трьохрозрядного двійкового лічильника тактових імпульсів таким чином.

Вхідна послідовна лінія зв'язку " Дані" підключається в контролері до послідовного входу рушійного регістра, а вхідна лінія " Синхронізація" - на керуючий вхід " Зрушення" рушійного регістра й на вхід лічильника тактових імпульсів. По черговому тактовому сигналі, що надійшов від синхрогенератора ЗП по лінії " Синхронізація", виконуються зрушення вмісту рушійного регістра на один розряд вліво й запис чергового біта даних з лінії зв'язку " Дані" у молодший розряд цього регістра. Одночасно збільшується на одиницю вміст лічильника тактових імпульсів. Як тільки вміст лічильника стає рівним 7, тобто в рушійний регістр прийняті послідовно вісім бітів інформації, формується керуючий сигнал " Запис", що забезпечує запис у буферний регістр чергового прийнятого байта з рушійного регістра. Цим же керуючим сигналом установлюється в " 1" регістр стану.

За час прийому в рушійний регістр наступних восьми бітів інформації байт даних з буферного регістра повинен бути переданий у шину даних системного інтерфейсу мікро-ЕОМ. При цій передачі скидається в нуль регістр стану контролера й нуль у цьому регістрі означає, що в рушійний регістр приймається з лінії зв'язку черговий байт інформації.

2.2 Організація асинхронного послідовного обміну даними із ЗП ускладнюється тим, що на передавальній і прийомній стороні послідовної лінії зв'язку використовуються настроєні на одну частоту, але фізично різні генератори тактових імпульсів й, отже, загальна синхронізація відсутня.

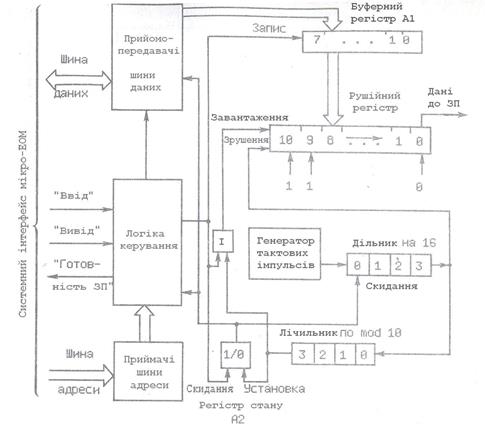

Контролер для асинхронної передачі даних у ЗП по послідовній лінії зв'язку (рис. 66.3) призначений для передачі даних у форматі із двома стоповими бітами. Після передачі чергового байта даних у регістр стану А2 записується 1. Одиничний вихідний сигнал регістра А2 інформує процесор про готовність контролера до прийому наступного байта даних і передачі його по лінії зв'язку у ЗП. Цей же сигнал забороняє формування імпульсів зі схеми вироблення імпульсів зрушення - дільника частоти сигналів тактового генератора на 16. Лічильник імпульсів зрушення (лічильник по mod 10) перебуває в нульовому стані, і його одиничний вихідний сигнал надходить на вентиль І, підготовляючи ланцюг вироблення сигналу завантаження рушійного регістра.

Процес передачі байта даних починається з того, що процесор, виконуючи команду " Вивід", виставляє цей байт на шині даних. Одночасно процесор формує керуючий сигнал системного інтерфейсу " Вивід ", по якому виконується запис переданого байта в буферний регістр А1, скидання регістра стану А2 і формування на вентилі І сигналу " Завантаження". Переданий байт посилається в розряди 1,..., 8 рушійного регістра, у нульовий розряд рушійного регістра записується 0 (стартовий біт), а в розряди 9 й 10 – 1 (стопові біти). Крім того, знімається сигнал " Скидання" з дільника частоти, він починає накопичувати імпульси генератора тактової частоти й у момент прийому шістнадцятого тактового імпульсу виробляє імпульс зрушення.

На вихідній лінії контролера " Дані" підтримується стан 0 (значення стартового біта) доти, доки не буде вироблений перший імпульс зрушення. Імпульс зрушення змінить стан лічильника імпульсів зрушення й перепише в нульовий розряд рушійного регістра перший інформаційний біт переданого байта даних. Стан, що відповідає значенню цього біта, буде підтримуватися на лінії " Дані" до наступного імпульсу зрушення.

Аналогічно будуть передані інші інформаційні біти, перший стоповий біт й, нарешті, другий стоповий біт, при передачі якого лічильник імпульсів зрушення знову встановиться в нульовий стан. Це приведе до запису 1 у регістр стану А2. Одиничний сигнал з виходу регістра А2 заборонить формування імпульсів зрушення, а також інформує процесор про готовність до прийому нового байта даних. Після завершення передачі чергового кадру (стартового біта, інформаційного байта й двох стопових бітів) контролер підтримує в лінії зв'язку рівень логічної одиниці (значення другого стопового біта).

Рівень логічної одиниці надходить по лінії " Дані" у контролер для асинхронного прийому даних (рис. 66.4). Цей рівень створює умови для створення сигналу, що забороняє роботу дільника частоти генератора тактових імпульсів. Дійсно, після прийому попереднього байта даних лічильник імпульсів зрушення (лічильник по mod 9) перебуває в нульовому стані й на вентиль І надходять два одиничних сигнали: з лічильника зрушень і з лінії " Дані". На виході вентиля І створюється сигнал скидання дільника частоти сигналів тактового генератора, що забороняє формування імпульсів зрушення.

У момент зміни стопового біта на стартовий біт (момент початку передавання нового кадру) на лінії " Дані" з'явиться рівень логічного нуля й тим самим зніметься сигнал скидання з дільника частоти. Стан 4-розрядного двійкового лічильника (дільника частоти) почне змінюватися. Коли на лічильнику буде значення 8, він видасть сигнал, що надходить на входи рушійного регістра й лічильника імпульсів зрушення. Тому що частота сигналів

генератора тактових імпульсів приймача повинна збігатися із частотою генератора тактових імпульсів передавача, то зрушення (зчитування) біта відбудеться приблизно на середині часового інтервалу, відведеного на передачу біта даних, тобто часу, необхідного для створення шістнадцяти тактових імпульсів. Це робиться для зменшення ймовірності помилки через можливе розходження частот генераторів передавача й приймача, перекручування форми переданих сигналів (перехідні процеси) і т.п. Наступне зрушення відбудеться після проходження шістнадцяти тактових імпульсів, тобто на середині часового інтервалу передачі першого інформаційного біта.

При прийомі в рушійний регістр дев'ятого біта кадру (восьмого інформаційного біта) з нього " висунеться" стартовий біт й, отже, у рушійному регістрі буде розміщений весь прийнятий байт інформації. У цей момент лічильник імпульсів зрушення прийде в нульовий стан і на його виході буде створений одиничний сигнал, по якому:

- вміст рушійного регістра перепишеться в буферний регістр;

- у регістр стану А2 запишеться 1 і він буде інформувати процесор про закінчення прийому чергового байта;

- вентиль І підготується до створення сигналу " Скидання" (цей сигнал сформується після приходу першого стопового біта).

Одержавши сигнал готовності (1 у регістрі А2), процесор виконає команду " Ввід". При цьому створюється керуючий сигнал системного інтерфейсу " Ввід", по якому виконуються пересилання прийнятого байта даних з буферного регістра в процесор (сигнал " Читання") і скидання регістра стану А2.

Обмін даними з ВУ по послідовних лініях зв'язку широко використається в сучасних мікро-ЕОМ, особливо в тих випадках, коли не потрібно високої швидкості обміну. Разом з тим застосування в мікро-ЕОМ послідовних ліній зв'язку із ЗП обумовлено двома важливими причинами. По-перше, послідовні лінії зв'язку прості по своїй організації: два проведення при симплексній і напівдуплексній передачі або чотири - при дуплексній. По-друге, у мікро-ЕОМ широко використовуються ЗП, обмін з якими необхідно вести в послідовному коді.

У сучасних мікро-ЕОМ застосовують, як правило, універсальні контролери для послідовного обміну, тобто що забезпечують як синхронний, так й асинхронний режим обміну даними із ЗП. Велике поширення одержали й ВІС - універсальні прийомопередавачі для послідовного обміну даними. Типовим прикладом такий ВІС є ВІС КР580ВВ51.

Домашнє завдання:

[5] С. 178-183.