Главная страница Случайная страница

КАТЕГОРИИ:

АвтомобилиАстрономияБиологияГеографияДом и садДругие языкиДругоеИнформатикаИсторияКультураЛитератураЛогикаМатематикаМедицинаМеталлургияМеханикаОбразованиеОхрана трудаПедагогикаПолитикаПравоПсихологияРелигияРиторикаСоциологияСпортСтроительствоТехнологияТуризмФизикаФилософияФинансыХимияЧерчениеЭкологияЭкономикаЭлектроника

Сучасні мікроконтролери в автоматизованих системах

|

|

План

Заняття № 1

1 Однокристальні мікроконтролери з CISC – архітектурою

2 ОМК на прикладі ВІС К1816ВЕ51

Заняття № 2

1 Однокристальні мікроконтролери з RISC – архітектурою

2 Архітектура РІС – контролерів

3 AVR – контролери

Заняття № 1

1 Однокристальним мікроконтролером (ОМК) називають пристрій, виконаний конструктивно в одному корпусі ВІС, що містить усі ним компоненти МПС: процесор, пам'ять даних, пам'ять програм, програмовані інтерфейси.

Однокристальним мікроконтролерам (ОМК) притаманні такі особливості:

ü система команд, зорієнтована на виконання задач керування і регулювання;

ü алгоритми, що реалізуються на ОМК, мають багато розгалужень залежно від зовнішніх сигналів;

ü дані, з якими оперують ОМК, не повинні мати велику розрядність;

ü схемна реалізація систем керування на базі ОМК нескладна і має невисоку вартість;

ü універсальність і можливість розширення функцій керування значно нижчі, ніж у системах з однокристальними МП.

Однокристальні мікроконтролери є зручним інструментом для створення сучасних вбудованих пристроїв керування різним обладнанням, наприклад, автомобільною електронікою, побутовою технікою, мобільними телефонами тощо.

CІSC (Complex Іnstructіon Set Computіng) - концепція проектування процесорів, що характеризується наступним набором властивостей:

ü нефіксованим значенням довжини команди;

ü виконання операцій, таких, як завантаження у пам’ять, арифметичні дії, кодується в одній інструкції;

ü невеликим числом регістрів, кожний з яких виконує строго певну функцію.

Типовими представниками є процесори на основі x86 команд (крім сучасного Іntel Pentіum 4, Pentіum D, Core, AMD Athlon, Phenom які є гібридними).

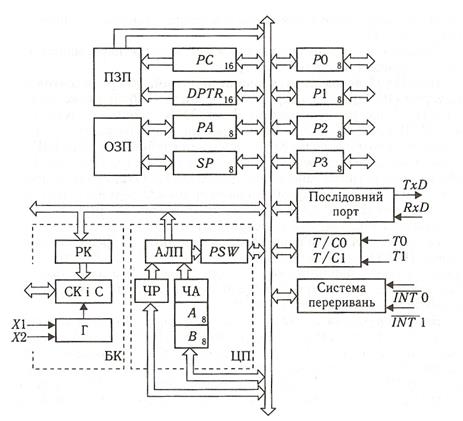

2 Структуру ОМК та функціонування основних блоків розглянемо на прикладі ВІС К1816ВЕ51 (рис. 1.1).

|

Структурна схема ОМК містить:

Ø блок 8-розрядного центрального процесора ЦП;

Ø пам'ять програм ПЗП ємністю 4 Кбайт;

Ø пам'ять даних ОЗП ємністю 128 байт;

Ø чотири 8-розрядних програмованих порти введення - виведення РО — РЗ;

Ø послідовний порт;

Ø два 16-розрядних програмованих таймери/лічильники Т/СО, Т/С1;

Ø систему переривань із п'ятьма векторами і двома рівнями пріоритетів;

Ø блок керування (БК).

Блок ЦП містить 8-розрядний АЛП, два акумулятори А і В, регістр слова стану процесора РSW (Processor State Word) та програмно-недоступні буферні регістри ЧА і ЧР, що виконують функції розподілу вхідних та вихідних даних АЛП. Центральний процесор виконує операції додавання, віднімання, множення, ділення, логічні операції І, АБО, НЕ, АБО-НЕ, операції зсуву і скидання. Він оперує з такими типами змінних: булевими (1 біт), цифровими (4 біт), байтовими (8 біт) та адресними (16 біт).

Акумулятор А є джерелом одного з операндів і місцем розміщення результату виконання багатьох команд. Деякі команди, наприклад, передавання інформації в/із ОЗП, команди ТЕSТ, ІNС, DЕС можуть виконуватися без участі акумулятора. Акумулятор В використовується як акумулятор лише в командах множення і ділення, а в інших випадках — як РЗП.

Регістр слова стану процесора РSW зберігає інформацію про стан АЛП у процесі виконання програми.

Постійний запам'ятовувальний пристрій, або резидента пам’ять програм (РПП), має інформаційну ємність 4 Кбайт і виконаний у вигляді ПЗП з програмною маскою. ПЗП має 16-розрядну адресну шину, що дає зміну розширити пам'ять до 64 Кбайт через під’єднання зовнішніх ВІС ПЗП. Адреса визначається вмістом лічильника команд РС (Рrоgrат Соипter) або вмістом регістра-покажчика даних DPTR (Data Роіпter Register).

Оперативний запам'ятовувальний пристрій, або резидентна пам'ять даних (РПД), складається з двох областей. Перша область — це ОЗПданих, що має інформаційну ємність 128 х 8 біт з адресами 0 — 7FH, друга область — регістри спеціальних функцій (SFR — Special Function Registers) з адресами 80H — FFН.

Оперативний запам'ятовувальний пристрій, або резидентна пам'ять даних (РПД), складається з двох областей. Перша область — це ОЗПданих, що має інформаційну ємність 128 х 8 біт з адресами 0 — 7FH, друга область — регістри спеціальних функцій (SFR — Special Function Registers) з адресами 80H — FFН.

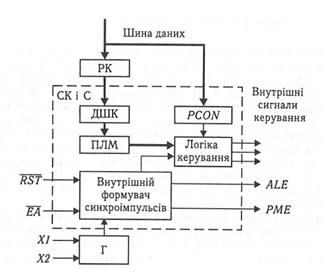

Блок керування (рис. 1.2) складається з генератора (Г) тактових сигналів програмно-недоступного регістра команд (РК) та схеми керування і синхронізації (СК і С). Код команди, зчитаної з РПП, запам'ятовується у 8-розрядному РК і надходить на дешифратор команд (ДШК), який входить до складу СК і С. Дешифратор команд формує 24-розрядний код, що надходить на програмовану логічну матрицю (ПЛМ), а після цього - на блок логіки керування.

Блок керування (рис. 1.2) складається з генератора (Г) тактових сигналів програмно-недоступного регістра команд (РК) та схеми керування і синхронізації (СК і С). Код команди, зчитаної з РПП, запам'ятовується у 8-розрядному РК і надходить на дешифратор команд (ДШК), який входить до складу СК і С. Дешифратор команд формує 24-розрядний код, що надходить на програмовану логічну матрицю (ПЛМ), а після цього - на блок логіки керування.

Блок логіки керування на підставі декодованого коду команди, зовнішніх керуючих сигналів  (сигналу загального скидання),

(сигналу загального скидання),  (сигналу блокування роботи з РПП) та сигналів від внутрішнього формувача імпульсів синхронізації виробляє внутрішні сигнали керування.

(сигналу блокування роботи з РПП) та сигналів від внутрішнього формувача імпульсів синхронізації виробляє внутрішні сигнали керування.

Внутрішній формувач імпульсів синхронізації формує:

§ внутрішні сигнали синхронізації машинних циклів;

§ вихідний сигнал дозволу фіксації адреси ALE;

§ сигнал дозволу програмної пам'яті РМЕ (формується лише під час роботи із зовнішньою пам'яттю).

У блок керування входить також регістр керування споживанням PCON (Power CONtrol).

Порти введення-виведення Р0 – Р3 призначені для забезпечення побайтного обміну інформацією ОМК із зовнішніми пристроями по 32 лініях введення-виведення.

Порт Р0 є двонапрямленим, оскільки через нього можна у будь-який момент вводити та виводити інформацію.

Порти Р1 — Р3 є квазідвонапрямленими, оскільки у будь-який момент через порти можна лише виводити інформацію. Для введення інформації слід записати в усі розряди регістра-фіксатора логічні одиниці. Після цього можна виконувати введення.

Послідовний порт призначений для забезпечення послідовного обміну даними. Його можна використовувати або як регістр зсуву, або як універсальний асинхронний приймач-передавач із фіксованою або змінною швидкістю обміну та із можливістю дуплексного режиму. Послідовний порт може працювати в одному з чотирьох режимів: (режим 0, режим 1, режим 2, режим 3). Послідовний порт програмується на один із режимів через запис керуючого слова в регістр SCON (Serial port CONtrol).

Блок таймерів-лічильників призначений для підрахунку зовнішніх подій (функція лічильника), реалізації програмно керованих затримок та виконання функцій задання часу (функція таймера). Під час виконання функції таймера вміст Т/С інкрементується в кожному машинному циклі, тобто через кожні 12 періодів резонатора. У процесі виконання і функції лічильника вміст Т/С інкрементується під впливом переходу зі стану логічної «1» у стан логічного «0» зовнішнього вхідного сигналу, що надходить на відповідний (Т0, Т1) вивід ОМК.

Вміст лічильника збільшується на одиницю, якщо у попередньому циклі надійшов вхідний сигнал високого рівня (1), а в наступному — сигнал низького рівня (0). Прапорці переповнення ТF0 і ТF1 встановлюються апаратно після переповнення відповідних Т/С (перехід вмісту регістра Т/С зі стану «всі одиниці» у стан «усі нулі»). Якщо при цьому переривання від відповідного Т/С дозволяється, то встановлення прапорця ТF викликає переривання. Скидання прапорців ТР0 і ТР1 відбувається апаратно під час передавання керування програмі оброблення відповідного переривання. Переривання прапорців ТF0 та ТР1 може відбуватися після виклику (встановлення ТF) або відміни (скидання ТF).

Система переривань призначена для реагування на зовнішні та внутрішні події. До зовнішніх подій належать появи нульового потенціалу (або зрізу) на виводах  ,

,  , до внутрішніх — переповнення таймерів-лічильників, завершення послідовного обміну. Зовнішні або внутрішні події викликають встановлення відповідних прапорців, що й спричиняють переривання. Прапорці можуть бути програмно встановлені або скинуті, при цьому їх програмне встановлення викликає переривання так само, як і реагування на подію. Отже, переривання можуть програмно викликатися або програмно усуватися.

, до внутрішніх — переповнення таймерів-лічильників, завершення послідовного обміну. Зовнішні або внутрішні події викликають встановлення відповідних прапорців, що й спричиняють переривання. Прапорці можуть бути програмно встановлені або скинуті, при цьому їх програмне встановлення викликає переривання так само, як і реагування на подію. Отже, переривання можуть програмно викликатися або програмно усуватися.

Заняття № 2

1 СІSС - мікроконтролери характеризуються досить розвиненою системою, наприклад, мікроконтролери серії і 80 х 51 мають 111 команд. Однак аналіз програм показав, що 20 % команд використовуються у 80 % випадків, а дешифратор команд займає понад 70 % усієї площі кристала. Тому у розробників МП виникла ідея скоротити кількість команд, придати їм єдиний формат і зменшити площу кристала, тобто використати RISC (Reduced Instruction Set Computer) архітектуру.

Особливістю контролерів, виконаних за RISC - архітектурою, є те, що всі команди виконуються за один-три такти, тоді як у СІSС - контролерах — за один-три машинних цикли, кожний із яких складається з кількох тактів, наприклад для i 80 х 51 — з 12 тактів. Тому RISC - контролери мають значно більшу швидкодію. Однак повніша система команд СІSС - контролерів у деяких випадках сприяє економії часу виконання певних фрагментів програми та економії пам'яті програм.

2 Типовими представниками RISC - процесорів є РІС-контролери (Periferial Interface Controller — контролери периферійних інтерфейсів) виробництва фірми «Microchip». РІС - контролери застосовують у системах високошвидкісного керування автомобільними й електричними двигунами, приладах побутової електроніки, телефонних приставках з АВН, системах охорони із повідомленням по телефонній лінії, міні - АТС. Окремі ВІС відрізняються розрядністю ПЗП: від 12 до 14 біт для серії РІС16Схх та 16 біт для серії РІС17Схх. Завдяки скороченій кількості команд (від 33 до 35) усі команди займають у пам'яті одне слово. Тривалість виконання кожної команди, крім команд розгалуження, становить чотири такти — один цикл (200 нс за частоти 20 МГц). Оперативний запам'ятовувальний пристрій виконано за схемою з довільною вибіркою та можливістю безпосередньої адресації у коді команди для будь-якого осередку. Стек реалізовано апаратно з глибиною 2, 8 або 16 осередків. Майже в усіх РІС-контролерах є система переривань, джерелом яких може бути таймер, а також зміна станів сигналів на деяких входах. У РІС-контролерах передбачено біт захисту ПЗП, що запобігає нелегальному копіюванню.

2 Типовими представниками RISC - процесорів є РІС-контролери (Periferial Interface Controller — контролери периферійних інтерфейсів) виробництва фірми «Microchip». РІС - контролери застосовують у системах високошвидкісного керування автомобільними й електричними двигунами, приладах побутової електроніки, телефонних приставках з АВН, системах охорони із повідомленням по телефонній лінії, міні - АТС. Окремі ВІС відрізняються розрядністю ПЗП: від 12 до 14 біт для серії РІС16Схх та 16 біт для серії РІС17Схх. Завдяки скороченій кількості команд (від 33 до 35) усі команди займають у пам'яті одне слово. Тривалість виконання кожної команди, крім команд розгалуження, становить чотири такти — один цикл (200 нс за частоти 20 МГц). Оперативний запам'ятовувальний пристрій виконано за схемою з довільною вибіркою та можливістю безпосередньої адресації у коді команди для будь-якого осередку. Стек реалізовано апаратно з глибиною 2, 8 або 16 осередків. Майже в усіх РІС-контролерах є система переривань, джерелом яких може бути таймер, а також зміна станів сигналів на деяких входах. У РІС-контролерах передбачено біт захисту ПЗП, що запобігає нелегальному копіюванню.

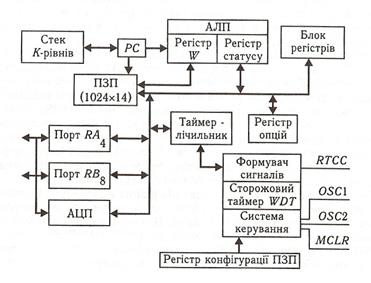

Архітектуру РІС-контролерів розглянемо на прикладі ВІС РІС16С71 (рис.2.1). Основою архітектури є роздільні шини та області пам'яті для даних і команд. Шина даних та осередок ОЗП є 8-розрядними, а шина команд і програмна пам'ять (ПЗП) — 14 - розрядними; 14-розрядна команда вибирається за один цикл. Двосхідчастий конвеєр забезпечує одночасне вибирання і виконання команди. Система команд містить 35 команд. Усі команди виконуються за один цикл, за винятком команд переходів, що виконуються за два цикли.

Структурна схема контролера містить:

ü восьмирівневий апаратний стек;

ü 13-розрядний програмний лічильник РС;

ü 8-розрядний АЛП;

ü ОЗП, який складається із 36-ти 8-розрядних РЗП;

ü 15 регістрів спеціальних функцій SFR (наприклад, регістр непрямої адресації W та регістри статусу, опцій і конфігурації ПЗП);

ü 8-розрядний таймер-лічильник із 8-розрядним програмним передподільником;

ü модуль АЦП з чотирма входами;

ü 13 ліній введення-виведення (чотирирозрядний порт RА, 8-розрядний порт RВ, лінія RТСС);

ü сторожовий таймер;

ü формувач зовнішнього сигналу RТСС або сигналу сторожового таймера;

ü система керування і синхронізації з внутрішнім генератором.

РІС - контролери за своїми параметрами конкурують з однокристальними мікро-ЕОМ та ОМК. Деякі модифікації РІС-контролерів мають] більшу швидкодію, ніж ОМК. РІС - контролери та ОМК застосовують і у вбудованих системах керування різного призначення.

3 Однокристальні АVR - мікроконтролери — це 8-розрядні високопродуктивні RISC - контролери загального призначення. Вони були створені групою розроблювачів дослідницького центру фірми «Atmel Соrр.» (Норвегія), ініціали яких сформували марку AVR. Особливістю AVR - мікроконтролерів є їх широка номенклатура, що дає змогу користувачу вибрати мікроконтролер із мінімальною апаратною надлишковістю і, отже, найменшої вартості. Так, у номенклатуру групи АТ90S входять прилади з ПЗП ємністю від 1 до 8 Кбайт із різними наборами периферії у корпусах із кількістю виводів від 8 до 48. Нині у серійному виробництві знаходяться три сімейства AVR — Тіnу, Classic і Меgа. Мікроконтролери Тіnу — найдешевші і мають найпростішу структуру, Меgа — найпотужніші, а Classic — займають проміжне положення між ними.

Система команд AVR налічує до 133 різних інструкцій. Розрізняють п'ять груп команд AVR: умовного розгалуження, безумовного розгалуження, арифметичні та логічні операції, команди пересилання даних, команди роботи з бітами. В останніх розробках AVR сімейства Меgа реалізована функція апаратного множення. За кількістю реалізованих і конструкцій AVR - мікроконтролерів більше використовують CISC процесори, ніж процесори RISС типу. У РІС - контролерів система команд налічує подібних до 75 різних інструкцій, а в МСS51 вона становить 111. Загалом прогресивна RISС -архітектура AVR у поєднанні із розширеною системою команд дає змогу створювати компактні програми з високою швидкістю виконання.

Домашнє завдання:

[8] с.446-457